PUBLICATIONS

Calibrating Charge Mismatch in a Baseline Correction Circuit

Chunbo Liu, Rafael Betancourt, Tae-Song Chung, Steve Chikin Lo, US Patent 9,778,804, October 3, 2017.Various embodiments provide a processing module that calibrates a current-mode baseline correction system to account for features in an input device that lead to “offset” in output of a charge integrator used for sensing presence of an input object. The offset is a difference between a common mode voltage, which is the average voltage output of the charge integrator over a sensing cycle and a mid-rail voltage midway between high and low power supply voltages. Calibration is performed by adjusting an N-side and/or P-side current flow duration parameter until common mode voltage falls within a low offset window in which the offset is deemed to be sufficiently close to the mid-rail voltage. The resulting duration parameters are stored and used for current-mode baseline corrections when operating an associated sensor electrode for capacitive sensing.

Multi-Step Incremental Switching Scheme

Zheming Li, Saikrishna Ganta, Tae-Song Chung, Rafael Betancourt, John Michael Wienerth, Farzaneh Shahrokhi, US Patent 9,740,351, August 22, 2017.A capacitance measurement circuit cancels background capacitance while reducing charge leakage and supply ripples during reset phases and integrate phases. The capacitance measurement circuit operates a first switch into a linear mode causing a first resistance in the first switch, and after a delay, operates a second switch into a saturation mode causing a second resistance in parallel to the first resistance.

System and method for measuring a capacitance and selectively activating an indicating transducer

Rafael Betancourt, US Patent 8,058,884, November 15, 2011.Systems and methods for sensing capacitances that are applicable to proximity sensor devices are provided. The systems and methods provide decreased implementation costs by reducing the number of output terminals required. Specifically, the systems and methods for sensing capacitances provide the ability to selectively activate indicating transducers, such as LEDs, with the same output terminals used for sensing capacitances. This reduces the need for additional, dedicated output terminals for activating the indicating transducers. As such, the system and method provides for efficient use of resources in proximity sensor devices.

Injection-locked Ring Oscillator Frequency Dividers

Rafael J. Betancourt-Zamora, Engineer’s Thesis, Stanford University, March 2005 (thesis)In this thesis, we propose a technique that has the potential of reducing the power dissipation of frequency division by up to an order of magnitude compared to conventional digital solutions by exploiting injection-locking in CMOS ring oscillators. Injection locking—the synchronization in frequency and phase of a free running oscillator with a source—is a mechanism that has been observed and studied since the early days of radio. In this work we use injection locking in differential CMOS ring oscillators to implement frequency prescalers that can operate at frequencies up to 2.8 GHz. We also present a low-power technique, the injection-locked loop, that extends the natural locking range of ring oscillator frequency dividers.

Noise Tutorial: Low-frequency CMOS Analog Design

Rafael Betancourt, Seminar at Synaptics, Inc., San Jose, California. Lecture given on May 16, 2002 (slides)

In this tutorial we stress the importance of noise performance in low-frequency instrumentation design and describe the types of noise present in integrated resistors and MOS devices. We present the noise trade-offs of different circuit topologies and provide examples on how to perform simple noise analysis.

How to Build a Radio on a Chip

Rafael Betancourt, White Paper, December 2001 (paper)

I study design techniques that will allow people to build inexpensive miniature radios with a single silicon chip and a couple of other small components. I also study ways of reducing the power consumption of such radios so that they may be used in portable devices that require a long battery life. I expect that this work will lead to new applications where miniature, low-cost radios will be incorporated into everyday devices and appliances. This will enable new, useful applications in areas such as ambulatory health monitoring, building & environmental monitoring, inventory management, wireless Internet access, and home and factory automation. I hope that the impact of small, inexpensive single-chip radios will be no less than that of the microprocessor revolution, which made microprocessor-controlled devices so pervasive in today’s world.

1-GHz and 2.8-GHz CMOS Injection-locked Ring Oscillator Prescalers

Rafael J. Betancourt-Zamora, Shwetabh Verma, Thomas H. Lee, Symposium on VLSI Circuits, Kyoto, Japan, June 14, 2001 (paper, slides) We implemented prescalers that can operate up to 2.8 GHz by exploiting the injection locking phenomena in differential CMOS ring oscillators. We tested a 5-stage, 1-GHz injection-locked modulo-8 prescaler fabricated in a 0.24-um CMOS technology that consumes 350 uW of power and occupies 0.012 mm2 of die area. The locking range is 20 MHz and the locked phase noise is -110 dBc/Hz @ 100 kHz. A 2.8-GHz, 3-stage, modulo-4 divider is also presented.

We implemented prescalers that can operate up to 2.8 GHz by exploiting the injection locking phenomena in differential CMOS ring oscillators. We tested a 5-stage, 1-GHz injection-locked modulo-8 prescaler fabricated in a 0.24-um CMOS technology that consumes 350 uW of power and occupies 0.012 mm2 of die area. The locking range is 20 MHz and the locked phase noise is -110 dBc/Hz @ 100 kHz. A 2.8-GHz, 3-stage, modulo-4 divider is also presented.

CMOS Injection-locked Ring Oscillator Prescalers

Rafael J. Betancourt-Zamora, Seminar at Texas A&M University, College Station, Texas. Lecture given on March 29, 2001 (slides)In this talk, we propose a technique that has the potential of reducing power dissipation of frequency division by up to an order of magnitude compared to conventional digital solutions. We exploited injection-locking in differential CMOS ring oscillators to implement prescalers that can operate at frequencies of up to 2.8 GHz. We also present a simplified model for injection-locked frequency dividers (ILFDs) that helps predict the locking range, and shows design insights that enable further optimization.

Integrated Spiral Inductor Calculator

Rafael J. Betancourt-Zamora, JavaScript program, January 14, 2000 (spiral.js, web)

Rafael J. Betancourt-Zamora, JavaScript program, January 14, 2000 (spiral.js, web)

The BioLink Implantable Telemetry System

Rafael J. Betancourt-Zamora, Technical Report, NASA-Ames Research Center Grant No. NGT2-52211, May 1999 (report) Most biotelemetry applications deal with the moderated data rates of biological signals. Few people have studied the problem of transcutaneous data transmission at the rates required by NASA’s Life Sciences-Advanced BioTelemetry System (LS-ABTS). Implanted telemetry eliminate the problems associated with wire breaking the skin, and permits experiments with awake and unrestrained subjects. Our goal is to build a low-power 174-216MHz RF transmitter suitable for short range biosensor and implantable use. A system architecture based on a Frequency-Locked Loop (FLL) Frequency Synthesizer is presented, and a novel differential frequency discriminator that eliminates the need for a frequency divider is also shown. A full system-level simulation of the FLL was performed and loop filter parameters were determined. The implantable antenna has been designed, simulated and constructed. An implant package compatible with the ABTS requirements is also being proposed. Extensive work performed at 200MHz in 0.5µm CMOS showed the feasibility of integrating the RF transmitter circuits in a single chip. The Hajimiri phase noise model was used to optimize the VCO for minimum power consumption. Two test chips were fabricated in a 0.5µm, 3V CMOS process. Measured phase noise for a 1.5mW, 200MHz ring oscillator VCO is -80dBc/Hz at 100KHz offset, showing good agreement with the theory.

Most biotelemetry applications deal with the moderated data rates of biological signals. Few people have studied the problem of transcutaneous data transmission at the rates required by NASA’s Life Sciences-Advanced BioTelemetry System (LS-ABTS). Implanted telemetry eliminate the problems associated with wire breaking the skin, and permits experiments with awake and unrestrained subjects. Our goal is to build a low-power 174-216MHz RF transmitter suitable for short range biosensor and implantable use. A system architecture based on a Frequency-Locked Loop (FLL) Frequency Synthesizer is presented, and a novel differential frequency discriminator that eliminates the need for a frequency divider is also shown. A full system-level simulation of the FLL was performed and loop filter parameters were determined. The implantable antenna has been designed, simulated and constructed. An implant package compatible with the ABTS requirements is also being proposed. Extensive work performed at 200MHz in 0.5µm CMOS showed the feasibility of integrating the RF transmitter circuits in a single chip. The Hajimiri phase noise model was used to optimize the VCO for minimum power consumption. Two test chips were fabricated in a 0.5µm, 3V CMOS process. Measured phase noise for a 1.5mW, 200MHz ring oscillator VCO is -80dBc/Hz at 100KHz offset, showing good agreement with the theory.

CMOS VCOs for Frequency Synthesis in Wireless Biotelemetry

Rafael J. Betancourt-Zamora and Thomas H. Lee, International Symposium on Low Power Electronics and Design, Monterey, California, August 10-12, 1998 (paper, poster)The Hajimiri phase noise model was used to optimize a differential ring VCO for minimum power consumption. We compare the phase noise performance of three buffer stages using clamped, symmetric and cross-coupled loads, respectively. We propose a cross-coupled buffer topology that achieves lower phase noise by exploiting symmetry. Measured phase noise for a 1.2mW, 150MHz VCO fabricated in 0.5um CMOS is -103.9dBc/Hz at 500KHz offset, showing good agreement with the theory.

Low Phase Noise CMOS Ring Oscillator VCOs for Frequency Synthesis

Rafael J. Betancourt-Zamora and Thomas H. Lee, 2nd International Workshop on Design of Mixed-Mode Integrated Circuits, Guanajuato, Mexico, July 27-29, 1998, pp. 37-40 (paper, slides)We propose a methodology that uses a new phase noise model to trade-off phase noise and power dissipation in the design of ring oscillators suitable for frequency synthesis. We compare the theoretical phase noise performance of three buffer stages using clamped, symmetric and cross-coupled loads, respectively. We propose a cross-coupled buffer topology that achieves lower phase noise by exploiting symmetry. This achieved a 20 times reduction in the 1/f3 corner frequency of the phase noise characteristic.

A Low Power Frequency Synthesizer for Wireless Biotelemetry

Rafael J. Betancourt-Zamora, 33rd. International Telemetering Conference, Las Vegas, Nevada, October 27-30, 1997 (slides)A system architecture based on a frequency-locked loop frequency synthesizer is presented, and a novel differential frequency discriminator that eliminates the need for a frequency divider is also proposed. A test chip was fabricated in a 0.5 um, 3V CMOS process.

A 1.5 mW, 200 MHz CMOS VCO for Wireless Biotelemetry

Rafael J. Betancourt-Zamora, Ali Hajimiri, and Thomas H. Lee, First International Workshop on Design of Mixed-Mode Integrated Circuits and Applications, Cancun, Mexico, July 28-30, 1997, pp. 72-74 (paper, slides)Our goal is to build a low-power 174-216 MHz RF transmitter suitable for short range biosensor and implantable use. A system architecture based on a frequency-locked loop frequency synthesizer is presented, and a novel differential frequency discriminator that eliminates the need for a frequency divider is also proposed. The Hajimiri phase noise model was used to optimize the VCO for minimum power consumption. A test chip was fabricated in a 0.5 um, 3V CMOS process. Measured phase noise for a 1.5 mW, 200 MHz ring oscillator VCO is -80 dBc/Hz at 100 kHz offset, showing good agreement with the theory.

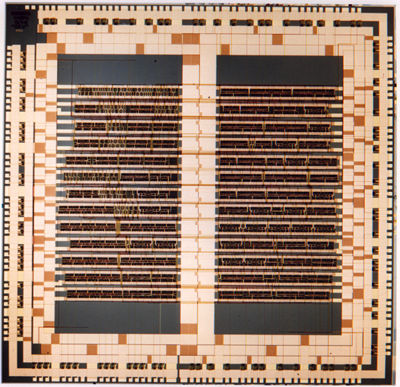

A High-speed GaAs Transversal Filter Circuit for Clutter Rejection Systems

Spencer White and Rafael J. Betancourt-Zamora, SPIE’s Tech. Symp. Optical Eng. & Photonics in Aerospace Sensing, April 1990 (paper) A high-speed GaAs Transversal Filter IC that has been designed at Hughes Aircraft Company and fabricated at AT&T Bell Laboratories is described. This circuit, which contains in excess of 41,000 transistors, implements a finite impulse response (FIR) filter for infrared data stream signal-to-noise ratio (SNR) enhancement in clutter rejection systems. The die is 9.1 mm on a side and dissipates 5.1 Watts. In addition this was implemented in a 1um GaAs HFET process with two layers of Ti/Pt/Au metallization.

A high-speed GaAs Transversal Filter IC that has been designed at Hughes Aircraft Company and fabricated at AT&T Bell Laboratories is described. This circuit, which contains in excess of 41,000 transistors, implements a finite impulse response (FIR) filter for infrared data stream signal-to-noise ratio (SNR) enhancement in clutter rejection systems. The die is 9.1 mm on a side and dissipates 5.1 Watts. In addition this was implemented in a 1um GaAs HFET process with two layers of Ti/Pt/Au metallization.